## **GF40: LVDS Pad Set**

### Libraries

| Name                      | Process CUP | Form<br>Factor |

|---------------------------|-------------|----------------|

| RGO_GF40_25V25_LP_UC_LVDS | LP yes      | staggered      |

### **Summary**

The LVDS I/O is a three-module design (input, output and reference block). The LDP\_OU\_675\_25V\_T is a 2GBit/s LVDS Driver, LDP\_IN\_675\_25V\_DN is a 2GBit/s LVDS Receiver and the LDP\_RE\_000\_25V is the voltage reference for up to 16 drivers. The LDP\_OU\_675\_25V\_T is designed to drive either  $50\Omega$  or  $100\Omega$  differential termination. This cell has been designed to meet a set of the standard LVDS specifications (IEEE Std 1596.3-1996, Low Voltage Differential Signaling).

Using this LVDS Pad Set, the system can achieve very high data rates per pin with simple termination requirements and low EMI. Both driver and receiver have been optimized for speed/power and can be ported to various pure digital CMOS processes from 0.18µm down to 28nm technologies. The LDP\_OU\_675\_25V\_T has been optimized for 2GBit/s operations. The receiver has been designed with no hysteresis in order to optimize sensitivity and skew.

The driver design has all the necessary components for transmit of LVDS data and a temperature stable internal reference for setting of the LVDS signaling voltage and common mode level. This provides user flexibility in deploying multiple LVDS transmitters. The reference block is required for the LVDS drivers to provide a stable common mode voltage as well as an accurate current reference for the driver source / sink current. Maximum operating frequency is 1GHz.

## **Absolute maximum ratings**

| Symbol           | Description                          | Value                             | Units |

|------------------|--------------------------------------|-----------------------------------|-------|

| $V_{VDD}$        | Core supply voltage range            | -0.5 to 1.38                      | V     |

| $V_{DVDD}$       | I/O supply voltage range             | -0.5 to 2.95                      | V     |

| V <sub>PAD</sub> | Voltage range at PAD                 | -0.5 to (V <sub>DVDD</sub> + 0.5) | V     |

| TJ               | Junction operating temperature range | -55 to 150                        | °C    |

### Recommended operating conditions

| Symbo             | ol Description                | Min   | Nom        | Max                     | Units |

|-------------------|-------------------------------|-------|------------|-------------------------|-------|

| $V_{VDD}$         | Core supply voltage           | 0.9   | 1.1 to 1.2 | 1.26                    | V     |

| $V_{DVDD}$        | I/O supply voltage            | 2.25  | 2.5        | 2.75                    | V     |

| V <sub>VREF</sub> | Reference voltage             |       |            |                         | V     |

| T <sub>A</sub>    | Ambient operating temperature | 0     | 25         | 100                     | °C    |

| TJ                | Junction temperature          | -40   | 25         | 125                     | °C    |

| V <sub>PAD</sub>  | Voltage at PAD                | -0.3V |            | V <sub>DVDD</sub> +0.3V | V     |

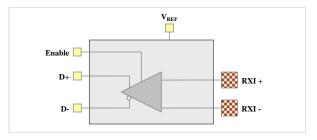

## LDP IN 675 25V DN: 1GHz LVDS Input

## **Key features:**

- Powered from 2.5V ±10% and 1.1V to 1.2V (±10%) core power supplies

- Operates up to 1GHz (2Gbps)

- Input receive sensitivity of 75mV peak differential (without hysteresis)

- Common mode range from 0V to 2.4V (limited by Power Supply)

- Power-up sequence independent

- Power consumption is 5 mW typical and 7.5 mW maximum at 1GHz

#### **AC Characteristics**

| Parameter                   | Тур | Max  | Units | Conditions                                                                                                     |

|-----------------------------|-----|------|-------|----------------------------------------------------------------------------------------------------------------|

| Propagation delay           | 0.5 | 0.85 | ns    | The slew rate for propagation<br>delays, duty cycle distortion<br>and maximum operating<br>frequency are 1V/ns |

| Maximum operating frequency | 1   |      | GHz   | All noise, jitter, and tdcd measured at 1GHz                                                                   |

| Maximum data rate           | 2   |      | Gb/s  |                                                                                                                |

# **GF40: LVDS Pad Set**

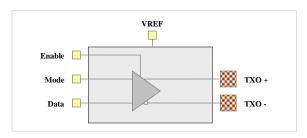

## LDP\_OU\_675\_25V\_T: 1GHz LVDS Output Pad

## **Key features:**

- Powered from 2.5V ±10% and 1.1V to 1.2V (±10%) core power supplies

- Operates up to 1GHz (2Gbps) with external 1 pF load

- Common mode output range 1.25 Volts ±50mV

- Power-up Sequence Independent

- Differential Skew between TXO\_P and TXO\_N 40ps

- Mode control for output drive control to drive either 100Ω or 50 Ω termination

- 0 = 3.25 mA (for 100Ω termination)

- $0 = 6.50 \text{ mA (for } 50\Omega \text{ termination)}$

- Power consumption at 1 GHz is 18.7 mW typical and 25.5 mW maximum

### **AC Characteristics**

| Symbol            | Description                                | Condition                          | Min | Тур | Max | Units |

|-------------------|--------------------------------------------|------------------------------------|-----|-----|-----|-------|

| t <sub>PHL</sub>  | Differential high to low propagation delay | $R_L = 100 \Omega$<br>$C_L = 1 pF$ |     | 500 | 730 | ps    |

| t <sub>PLH</sub>  | Differential low to high propagation delay | $R_L = 100 \Omega$<br>$C_L = 1 pF$ |     | 500 | 730 | ps    |

| t <sub>rise</sub> | V <sub>OD</sub> differential rise time     | 20% to 80%                         | 120 | 190 | 250 | ps    |

| t <sub>fall</sub> | V <sub>OD</sub> differential fall time     | 20% to 80%                         | 120 | 190 | 250 | ps    |

### **Characterization Corners**

| Nominal VDD | Model | VDD     | DVDD = 2.5V | Temperature |

|-------------|-------|---------|-------------|-------------|

|             | FF    | +5%     | +10%        | -40°C       |

|             | FF    | +5%     | +10%        | 125°C       |

| 1.2         | TT    | nominal | nominal     | 25°C        |

|             | SS    | -10%    | -10%        | -40°C       |

|             | SS    | -10%    | -10%        | 125°C       |

| 1.1         | FF    | +10%    | +10%        | -40°C       |

|             | FF    | +10%    | +10%        | 125°C       |

|             | TT    | nominal | nominal     | 25°C        |

|             | SS    | -10%    | -10%        | -40°C       |

|             | SS    | -10%    | -10%        | 125°C       |

## **Cell summary**

| Name              | Description                                  |

|-------------------|----------------------------------------------|

| LDP_IN_675_25V_DN | 1GHz LVDS input cell                         |

| LDP_OU_675_25V_T  | 1GHz LVDS output cell                        |

| LDP_RE_000_25V    | V <sub>REF</sub> pad                         |

| PVP_VD_RCD_12V    | Core power pad with VREF                     |

| PVP_VS_RCD_12V    | Power pad for VSS with VREF bus              |

| PVP_VD_PDO_25V    | Driver power pad with POC control            |

| PVP_VD_RDO_25V    | Driver power pad                             |

| PVP_VS_RDO_25V    | I/O ground supply with VREF bus              |

| SVP_SP_001_25V    | 0.1 µm spacer                                |

| SVP_SP_001_25V    | 1 µm spacer                                  |

| SVP_SP_005_25V    | 5 μm spacer                                  |

| SVP_SP_010_25V    | 10 µm spacer                                 |

| SPP_RS_005_25V    | DVDD, DVSS, POC, BIAS and VREF rail splitter |

| SPC_SPC_AD_UN     | Core limited library adapter pad             |

## Physical sizes

| Pad name          | Width | Height <sup>[*]</sup> | Units |

|-------------------|-------|-----------------------|-------|

| LDP_RE_000_18V    | 37    | 180                   | μm    |

| LDP_IN_675_25V_DN | 55    | 180                   | μm    |

| LDP_OU_675_25V_T  | 55    | 180                   | μm    |

| PVP_VD_RCD_12V    | 20    | 180                   | μm    |

| PVP_VS_RCD_12V    | 20    | 180                   | μm    |

| PVP_VD_PDO_25V    | 20    | 180                   | μm    |

| PVP_VD_RDO_25V    | 20    | 180                   | μm    |

| PVP_VS_RDO_25V    | 20    | 180                   | μm    |

| SVP_SP_000_25V    | 0.1   | 180                   | μm    |

| SVP_SP_001_25V    | 1     | 180                   | μm    |

| SVP_SP_005_25V    | 5     | 180                   | μm    |

| SVP_SP_010_25V    | 10    | 180                   | μm    |

| SPP_RS_005_25V    | 5     | 180                   | μm    |

| SPP_SPC_AD_UN     | 25    | 180                   | μm    |

[\*] Includes CUP bond opening.

### © 2006-2011 Aragio Solutions. All rights reserved.

Information in this document is subject to change without notice. Aragio Solutions may have patents, patent applications, trademarks, copyrights or other intellectual property rights covering subject matter in this document. Except as expressly provided in any written license agreement from Aragio, the furnishing of this document does not give you any license to the patents, trademarks, copyrights, or other intellectual property.

Published by:

Aragio Solutions

2201 K Avenue

Section B Suite 200

Plano, TX 75074-5918

Phone: (972) 516-0999

Fax: (972) 516-0998

Web: http://www.aragio.com/

While every precaution has been taken in the preparation of this book, the publisher assumes no responsibility for errors or omissions, or for damages resulting from the use of the information contained herein. This document may be reproduced and distributed in whole, in any medium, physical or electronic, under the terms of a license or nondisclosure agreement with Aragio.

Printed in the United States of America