#### Libraries

| Name                           | Process | Form<br>Factor |

|--------------------------------|---------|----------------|

| RGO_TSMC16_18V33_FFC_40C_RF    | FFC     | Inline CUP     |

| RGO_TSMC12_18V33_FFC_LL_40C_RF | FFC_LL  | Inline CUP     |

### Summary

The RF library provides Analog / RF I/O cells including LNA input pads, a 5V tolerant PA output pad and a 10GHz analog signal pad with multiple input resistance options. Discrete components (RF diodes and SCR's) are provided to enable construction of a custom ESD protection solution.

These libraries are offered at both 16nm and a 12nm shrink. They are available in an inline CUP wire bond implementation with a flip chip option.

#### **ESD Protection:**

- JEDEC compliant

- 2KV ESD Human Body Model (HBM)

- 500 V ESD Charge Device Model (CDM)

#### Latch-up Immunity:

- JEDEC compliant

- Tested to I-Test criteria of  $\pm 100$ mA @ 125°C

## **RF Diodes**

A set of PPLUS\_NWELL\_DIODE RF diodes provide minimum capacitance for RF applications and high current handling capability for good ESD protection.

## Silicon-Controlled Rectifiers (SCR)

A set of P+ to Nwell SCR discrete components provide the lowest capacitance with the highest ESD protection. These components have been used in I/O pads to demonstrate over 6KV ESD protection.

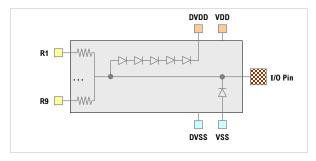

## ANP\_BI\_DWR\_5T

ANP\_BI\_DWR\_5T is a bi-directional analog signal pad with selectable input resistance. Resistors R1 to R4 and R6 to R9 can be used in parallel to achieve the desired resistance value as low as 1.3 ohms.

This structure can then be used with output amplifiers for which R5 can be used in the feedback path. If used in this manner, R1 to R4 and R6 to R9 should be individually connected to isolated fingers of the driver transistors.

## Analog / RF Pads

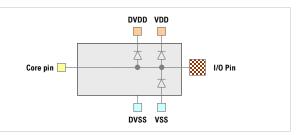

# ANP\_IN\_LNA\_1033V

ANP\_IN\_LNA\_10V is a 0 to 0.8V analog I/O pad optimized for low capacitance and designed to protect thin gate oxide input devices. The layout uses wide metal 3 interconnect (14  $\mu$ m) for low inductance from the bond pad to the core. Additional variants (\_UVT & \_OVT) provide lower capacitance and the ability to handle occasional signal undershoot / overshoot of 0.7V.

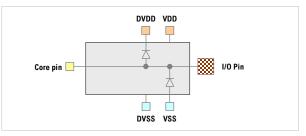

## ANP\_IN\_LNA\_33V

ANP\_IN\_LNA\_33V is a 0 to 3.3V analog I/O pad optimized for low capacitance. The layout uses wide metal 3 interconnect (12  $\mu m$ ) for low inductance from the bond pad to the core.

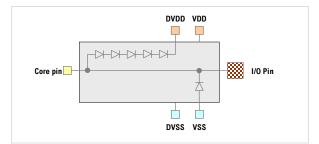

## ANP\_OU\_PWA\_5T

ANP\_OU\_PWA\_5T is an analog I/O pad optimized for low capacitance which uses SCRs for ESD clamp devices.

The stacked diode ESD structure from DVDD to the I/O pin provides extended overvoltage protection. With a 3.3V power supply, this I/O pad is 5V tolerant. Dropping to an I/O domain power supply of 1.8V, the pad is 3.3V tolerant.

# **Recommended operating conditions**

|       | -                    |                        |      |                        | -     |

|-------|----------------------|------------------------|------|------------------------|-------|

|       | Description          | Min                    | Nom  | Max                    | Units |

| Vvdd  | Core supply voltage  | 0.72                   | 0.80 | 0.88                   | V     |

| Vdvdd | I/O supply voltage   | 2.97                   | 3.3  | 3.63                   | V     |

|       |                      | 2.25                   | 2.5  | 2.75                   | V     |

|       |                      | 1.62                   | 1.8  | 1.98                   | V     |

|       |                      | 1.08                   | 1.2  | 1.32                   | V     |

| TJ    | Junction temperature | -40                    | 25   | 125                    | °C    |

| VPAD  | Voltage at PAD       | V <sub>DVSS</sub> -0.3 | -    | V <sub>DVDD</sub> +0.3 | V     |

# **Characterization Corners (16nm)**

| Model                             | LPE Type         | VDD=0.8V | <b>DVDD</b> [1] | Temp  |  |

|-----------------------------------|------------------|----------|-----------------|-------|--|

| FFGNP                             | Cbest_CCbest_T   | +10%     | +10%            | -40°C |  |

| FFGNP                             | Cbest_CCbest_T   | +10%     | +10%            | 0°C   |  |

| FFGNP                             | Cbest_CCbest_T   | +10%     | +10%            | 125°C |  |

| FFG                               | Ctypical         | +10%     | +10%            | 125°C |  |

| TT                                | Ctypical         | nominal  | nominal         | 25°C  |  |

| TT                                | Ctypical         | nominal  | nominal         | 85°C  |  |

| SSGNP                             | Cworst_CCworst_T | -10%     | -10%            | -40°C |  |

| SSGNP                             | Cworst_CCworst_T | -10%     | -10%            | 0°C   |  |

| SSGNP                             | Cworst_CCworst_T | -10%     | -10%            | 125°C |  |

| (11) D/DD = 1.2V 1.8V 2.5V & 3.3V |                  |          |                 |       |  |

[1] DVDD = 1.2V, 1.8V, 2.5V & 3.3V

## **Characterization Corners (12nm)**

| Model | LPE Type       | VDD=0.8V | <b>DVDD</b> [1] | Temp  |

|-------|----------------|----------|-----------------|-------|

| FF    | Cbest_CCbest   | +10%     | +10%            | -40°C |

| FF    | Cbest_CCbest   | +10%     | +10%            | 0°C   |

| FF    | Cbest_CCbest   | +10%     | +10%            | 125°C |

| FFG   | Ctypical       | +10%     | +10%            | 125°C |

| TT    | Ctypical       | nominal  | nominal         | 25°C  |

| TT    | Ctypical       | nominal  | nominal         | 85°C  |

| SS    | Cworst_CCworst | -10%     | -10%            | -40°C |

| SS    | Cworst_CCworst | -10%     | -10%            | 0°C   |

| SS    | Cworst_CCworst | -10%     | -10%            | 125°C |

[1] DVDD = 1.2V, 1.8V, 2.5V & 3.3V

#### © 2010-2018 Aragio Solutions. All rights reserved.

Information in this document is subject to change without notice. Aragio Solutions may have patents, patent applications, trademarks, copyrights or other intellectual property rights covering subject matter in this document. Except as expressly provided in any written license agreement from Aragio, the furnishing of this document does not give you any license to the patents, trademarks, copyrights, or other intellectual property.

Published by:

Áragio Solutions

2201 K Avenue

Section B Suite 200

Plano, TX 75074-5918

Phone:

(972) 516-0999

Fax:

(972) 516-0998

Web:

http://www.aragio.com/

While every precaution has been taken in the preparation of this book, the publisher assumes no responsibility for errors or omissions, or for damages resulting from the use of the information contained herein.

Printed in the United States of America